Spoločnosť IBM v spolupráci so svojimi partnermi Globalfoundries a Samsung vyvinula podľa spoločnosti prvý praktický výrobný proces, ktorý sa bude dať použiť na výrobu čipov 5-nm výrobným procesom.

Kľúčovým prvkom nového výrobného procesu je úplne nová konštrukcia tranzistora, ktorá zlepšuje vlastnosti doterajších tranzistorov a je použiteľná aj pri ich zmenšení pod súčasné veľkosti.

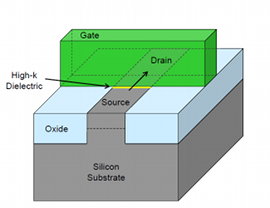

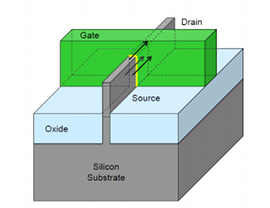

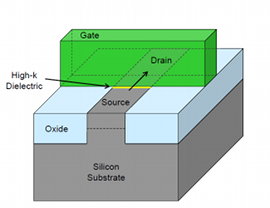

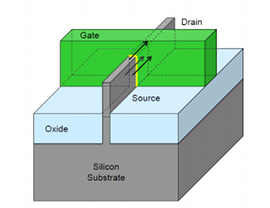

U tranzistorov bolo donedávna hradlo položené na kanáli spájajúcom emitor a kolektor, dotykovú styčnú plochu tvorila len jedna strana hradla. S 22-nm procesom sa prešlo na tzv. FinFET konštrukciu, pri ktorej je kanál vystúpený a hradlo ho obkolesuje z troch strán. To umožňuje aj pri zmenšení tranzistora udržať alebo zvýšiť styčnú plochu. Pri tejto konštrukcii sa typicky používa viac navzájom sa križujúcich kanálov a hradiel.

U 5-nm procesu už ale typicky pre kremíkové tranzistory nebude stačiť ani takáto konštrukcia respektíve by neviedla k zlepšeniu parametrov čipov.

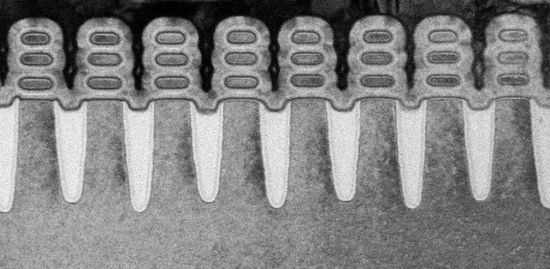

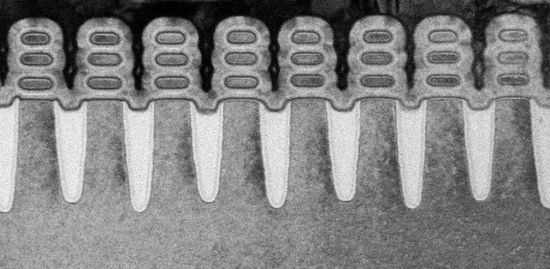

Sken tranzistorov vyrobených novým procesom, kliknite pre zväčšenie (foto: IBM)

IBM preto prišla s konštrukciou označovanou spoločnosťou ako tranzistory s kremíkovými nanoplátmi, u ktorých je kanál kompletne obalený hradlom. Konštrukcia čipu pozostáva z viacerých vrstiev kremíkových nanoplátov.

Presný 3D model umožňujúci si konštrukciu predstaviť IBM zatiaľ nezverejnila, prirovnáva ju ale k otočeniu styčnej oblasti FinFET tranzistora nabok.

Doterajšia konštrukcia tranzistorov, pôvodné planárne (vľavo) a aktuálne FinFET, kliknite pre zväčšenie (obrázok: Intel)

Na rozdiel od rozličných experimentálnych technológií používajúcich úplne nové materiály a úplne iné štruktúry sú čipy novej technológie vyrobiteľné technológiou EUV, Extreme Ultraviolet, litografie, ktorá sa pripravuje na nasadenie u jednotlivých výrobcov čipov. Zrejme tak ide o praktický výrobný proces a konštrukciu tranzistorov, či ich výrobcovia nasadia zatiaľ nie je známe.

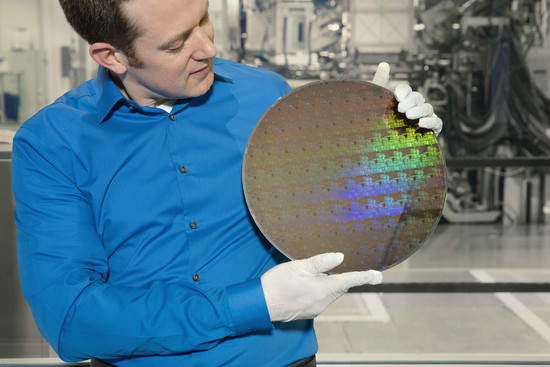

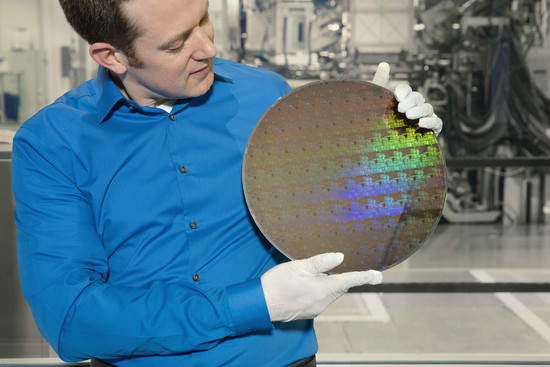

Plán s čipmi vyrobenými novým procesom, kliknite pre zväčšenie (foto: Connie Zhou / IBM)

IBM v každom prípade už vyrobila novým výrobným procesom testovacie čipy, pričom oproti pripravovanému 7-nm procesu dosiahla o 50% vyššiu hustotu tranzistorov, konkrétne 30 miliárd oproti 20 miliardám na čipe "veľkosti nechta".

5-nm čipy vyrobené takýmto spôsobom umožnia oproti súčasným najlepším 10-nm podľa IBM dosiahnuť o 40% lepší výkon pri rovnakej spotrebe alebo o 75% nižšiu spotrebu pri rovnakom výkone.

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

masne ruky preč

Od: odolnosť

|

Pridané:

5.6.2017 9:55

Nekýchaj, lebo mi zoskratuješ obvod.

|

| |

Re: masne ruky preč

Od: Reikii

|

Pridané:

5.6.2017 10:18

tak schudni

|

| |

asitak

Od: delyb

|

Pridané:

5.6.2017 10:21

je to dobre konecne pojde cena dole na bitcoin super

|

| |

Re: asitak

Od: Sak ja ne?

|

Pridané:

5.6.2017 13:28

BTC sa ťaží cez ASIC čo je špecializovaný HW ktorý ťaží niekoľkonásobne rýchlejšie ako najvýkonnejšie počítače sveta... čiže nie... si 4 roky pozadu

|

| |

Re: asitak

Od: Okauyyy

|

Pridané:

5.6.2017 18:42

A ASIC sa nepouzivaju tranzistory?

|

| |

Re: asitak

Od: qwkrieerer

|

Pridané:

5.6.2017 20:00

Nie tam sa pouzivaju pnp a npn polovodice.

|

| |

Titulcancel

Od: syntaxterrorXXX

|

Pridané:

5.6.2017 10:52

Ked uz pri skusani predoslej generacie zakaznikovy trebalo pomaly lupou pozerat, ci ho nechcu o...kabatit, teraz je uz priekazne evidentne, k odstraneniu ktoreho "rusiveho" elementu vyrobneho cyklu proces smeruje.

|

| |

Re: Titulcancel

Od reg.: Sheep

|

Pridané:

5.6.2017 11:05

Lepi ti co, ze si kupis 5nm procak a bude pomaly :)

|

| |

Re: Titulcancel

Od: Menovec

|

Pridané:

5.6.2017 11:37

Nie pomalý, ale že ho nenájde vo vrecku...

|

| |

?????

Od: psycho38

|

Pridané:

5.6.2017 11:38

mne dost vadia taketo nepresne informacie..

"konkrétne 30 miliárd oproti 20 miliardám na čipe "veľkosti nechta"."

velkosti ktoreho nechta? malicka alebo palca na nohe? aka je statisticky priemerna plocha nechta? hanba...

|

| |

Re: ?????

Od: userrr

|

Pridané:

5.6.2017 11:49

Mne sa pacia prepocty na futbalove ihriska alebo hamburgery.

|

| |

Re: ?????

Od: Menovec

|

Pridané:

5.6.2017 12:08

Alebo na tvoj chlp.

|

| |

Re: ?????

Od: ffdf

|

Pridané:

5.6.2017 12:54

a čo on je pitcha?

|

| |

Re: ?????

Od: Mxxl

|

Pridané:

5.6.2017 12:09

mne zas prepočty na veľkosť mince.. neviem prečo ale vždy si predstavím 10 korunáčku a pritom možno myslia 1 euro cent

|

| |

ibmmm

Od: nomi

|

Pridané:

5.6.2017 12:11

konečne budú tie čípky menšie

|

| |

.......................

Od: tenodtal

|

Pridané:

5.6.2017 12:22

5nm

MOC

VELA

MALE

:D

|

| |

hmm, pekne

Od: qw11

|

Pridané:

5.6.2017 13:31

"vyššiu hustotu tranzistorov, konkrétne 30 miliárd oproti 20 miliardám na čipe"

Pozeral som teraz na GME stoji tranzistor priblizne 0.8EUR. Ak by takyto cip dala nasa vlada rozobrat a rozpredala ho na suciastky tak mame splateny dlh a este bude aj z coho kradnut. :D

Kaslat na bitcoin, kto ide do toho?

|

| |

tranzistor

Od: toro

|

Pridané:

5.6.2017 16:07

len pripomínam, že výrazy kolektor a emitor sa používali pri bipolárnych tranzistoroch.

|

| |

Re: tranzistor

Od: Menovec

|

Pridané:

6.6.2017 8:49

A zrovna tak aj pri unipolárnych tranzistoroch.

|